SPI

SPI는 Serail Peripheral Interface Bus의 약어로 마이크로컨트롤러와 시프트 레지스터, 센서, SD 카드와 같은 소형 주변 장치 간에 데이터를 전송하는 데 일반적으로 사용되는 인터페이스 버스입니다.

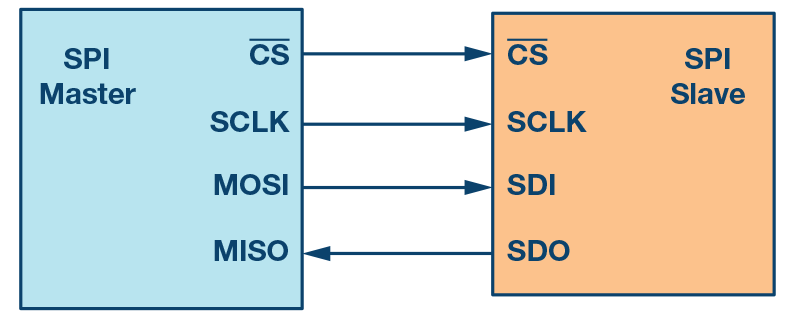

SPI 통신은 4개의 신호단자로 구성되어 있습니다.

| 신호단자 이름 | 다른 이름 | 설명 |

| SCLK | SCK, CLK | Serial Clock |

| MOSI | SDI, DI, SI | Master Output Slave Input |

| MISO | SDO, DO, SO | Slave Output Master Input |

| SS | nCS, CS, nSS, STE, CE | Slave Select, Chip Enable |

- SCLK: 직렬 클럭 (마스터로부터의 출력)

- MOSI; SIMO: 마스터 출력, 슬레이브 입력 (마스터로부터의 출력)

- MISO; SOMI: 마스터 입력, 슬레이브 출력 (슬레이브로부터의 출력)

- SS: 슬레이브 장치를 선택하여 통신 (active low, 마스터로부터의 출력).

클럭 신호를 생성하는 장치를 마스터라고 하고. 마스터와 슬레이브 간에 전송되는 데이터는 마스터에서 생성된 클럭에 동기화됩니다. SPI 인터페이스는 하나의 마스터만 가질 수 있고 하나 또는 여러 개의 슬레이브를 가질 수 있습니다. 마스터의 칩 선택 신호는 슬레이브를 선택하는 데 사용됩니다. 여러 개의 슬레이브를 사용하는 경우 마스터에서 각 슬레이브에 대한 개별 칩 선택 신호가 필요합니다.

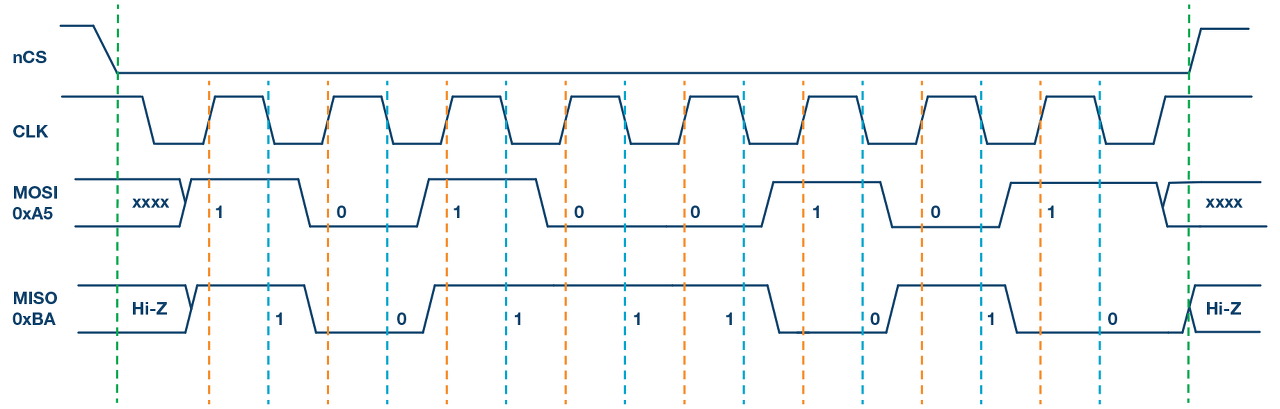

MOSI 및 MISO는 데이터 라인입니다. MOSI는 마스터에서 슬레이브로 데이터를 전송하고 MISO는 슬레이브에서 마스터로 데이터를 전송합니다.

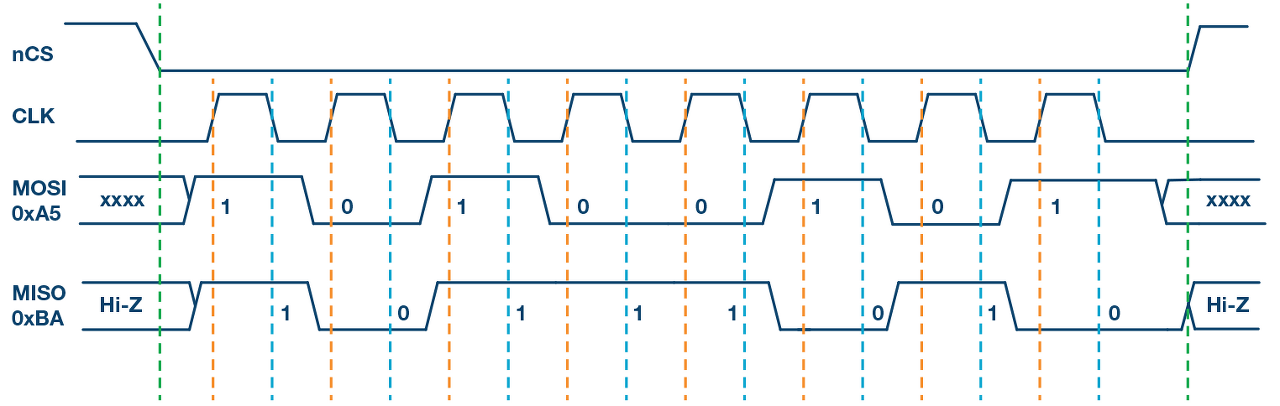

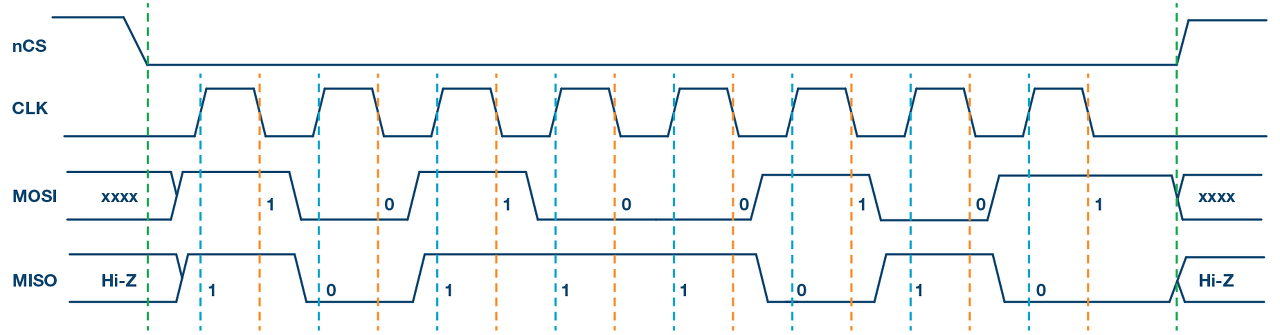

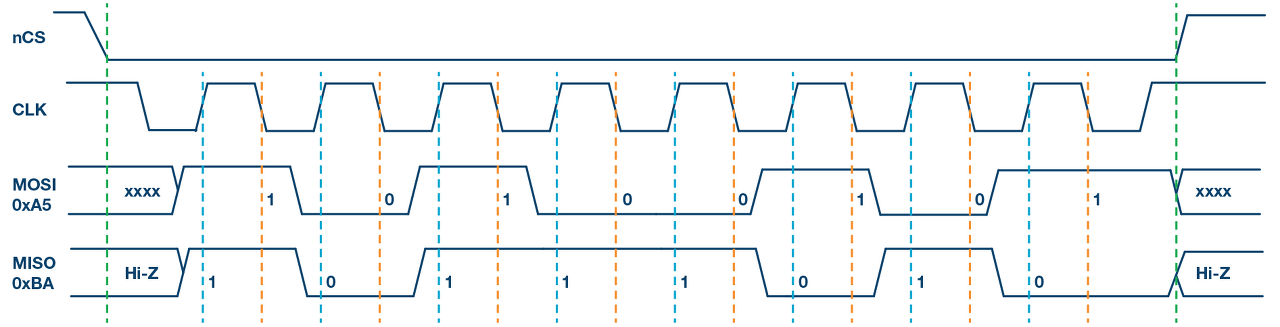

SPI통신은 클럭의 극성(Clock Polarity, CPOL)과 위상(Clock Phase, CPHA)에 따라 4가지 모드가 있습니다.

| SPI 모드 | CPOL | CPHA |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 1 |

| 3 | 1 | 0 |

CPOL : SPI 버스가 유휴 상태 동안 클록 신호의 극성을 설정합니다. 유휴 상태는 CS가 하이로 전송 시작 시 로우로 전환되고 CS가 로우에서 전송 종료 시 하이로 전환되는 기간 으로 정의 됩니다 . CPOL = 0이면 비활성 상태일 때 SCK = LOW값을 가지며, CPOL = 1이면 비활성 상태일 때 SCK = HIGH 값을 가집니다.

CPHA : 클럭 위상을 선택합니다. CPHA = 0이면 데이터는 비활성 상태에서 활성 상태로 바뀌는 에지에서 샘플링 되고, CPHA = 1 이면 데이터는 활성상태에서 비활성상태로 바뀌는 에지에서 샘플링 됩니다.

SPI 모드 1, CPOL = 0, CPHA = 1: CLK 유휴 상태 = 낮음, 데이터는 하강 에지에서 샘플링되고 상승 에지에서는 이동

SPI 모드 2, CPOL = 1, CPHA = 1: CLK 유휴 상태 = 하이, 데이터는 하강 에지에서 샘플링되고 상승 에지에서 이동

SPI 모드 2, CPOL = 1, CPHA = 1: CLK 유휴 상태 = 하이, 데이터는 하강 에지에서 샘플링되고 상승 에지에서 이동

SPI 모드 3, CPOL = 1, CPHA = 0: CLK 유휴 상태 = 높음, 데이터는 상승 에지에서 샘플링되고 하강 에지에서는 이동

다중 슬레이브

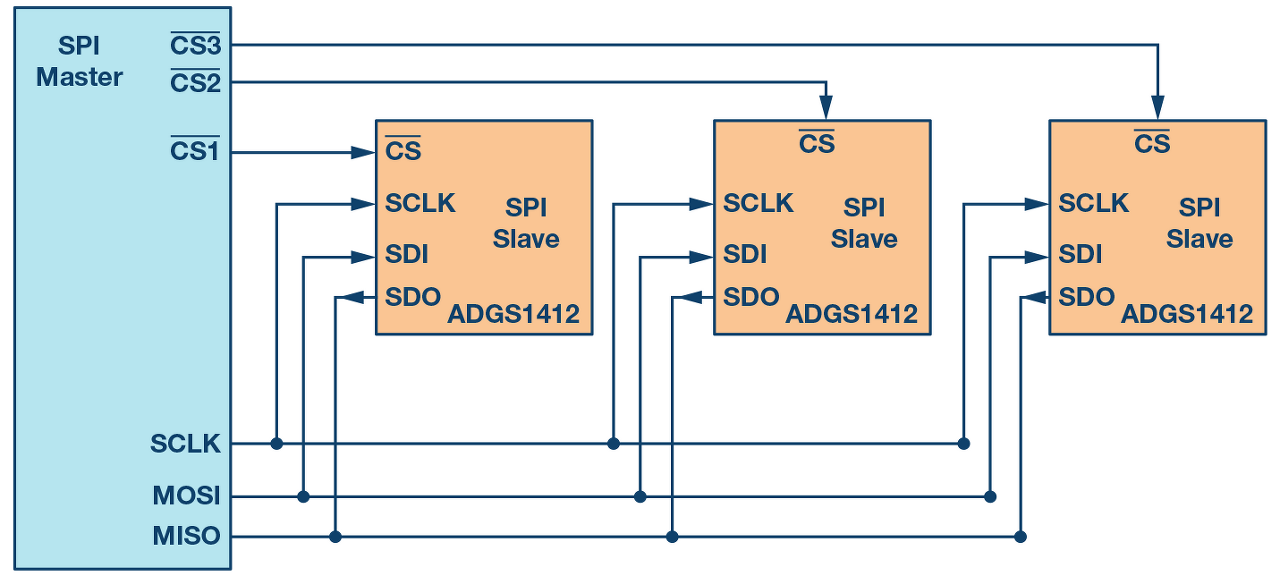

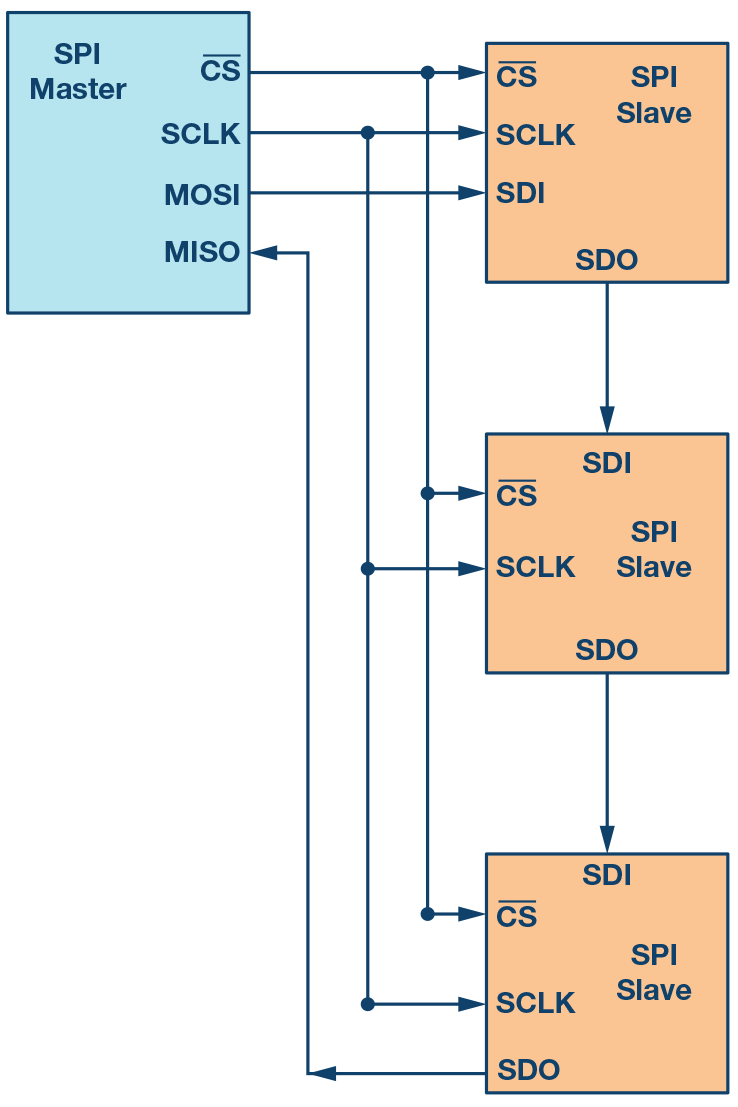

여러 슬레이브를 단일 SPI 마스터와 함께 사용할 수 있습니다. 슬레이브는 일반 모드 또는 데이지 체인 모드로 연결할 수 있습니다.

일반 모드에서는 마스터에서 각 슬레이브에 대한 개별 칩 선택이 필요합니다. 칩 선택 신호가 마스터에 의해 활성화되면 MOSI/MISO 라인의 클록 및 데이터는 선택한 슬레이브에 사용할 수 있습니다. 다중 칩 선택 신호가 활성화되면 마스터가 데이터를 전송하는 슬레이브를 식별할 방법이 없기 때문에 MISO 라인의 데이터가 손상됩니다.

슬레이브의 수가 증가할수록 마스터로부터의 칩 선택 라인의 수도 증가한다. 이는 마스터에서 필요한 입력 및 출력 수를 빠르게 추가하고 사용할 수 있는 슬레이브 수를 제한할 수 있습니다.

데이지 체인 모드에서 슬레이브는 모든 슬레이브에 대한 칩 선택 신호가 함께 연결되고 데이터가 한 슬레이브에서 다음 슬레이브로 전파되도록 구성됩니다. 이 구성에서 모든 슬레이브는 동시에 동일한 SPI 클록을 수신합니다. 마스터의 데이터는 첫 번째 슬레이브에 직접 연결되고 해당 슬레이브는 다음 슬레이브에 데이터를 제공하는 식입니다.

장점

- 완전한 전이중(Full duplex) 통신

- 전송되는 비트에 대한 완전한 프로토콜 유연성

-

전송기가 필요하지 않다.

- 최대 클럭이 제한되지 않아 속도 제한이 없다.

단점

- 하드웨어 슬레이브 인식이 없음

- 오류 검사 프로토콜이 정의되어 있지 않음

- 일반적으로 노이즈 스파이크에 영향을 받는 경향이 있음 (통신 문제를 일으킬 수 있음)

- 하나의 마스터 장치만 지원.

- 다른 통신 방식보다 더 많은 신호선(선)이 필요함.

'통신' 카테고리의 다른 글

| CAN (0) | 2022.03.01 |

|---|---|

| LoRa (0) | 2022.02.15 |

| WIFI (0) | 2022.02.14 |

| Bluetooth (0) | 2022.02.14 |

| I2C (0) | 2022.02.11 |