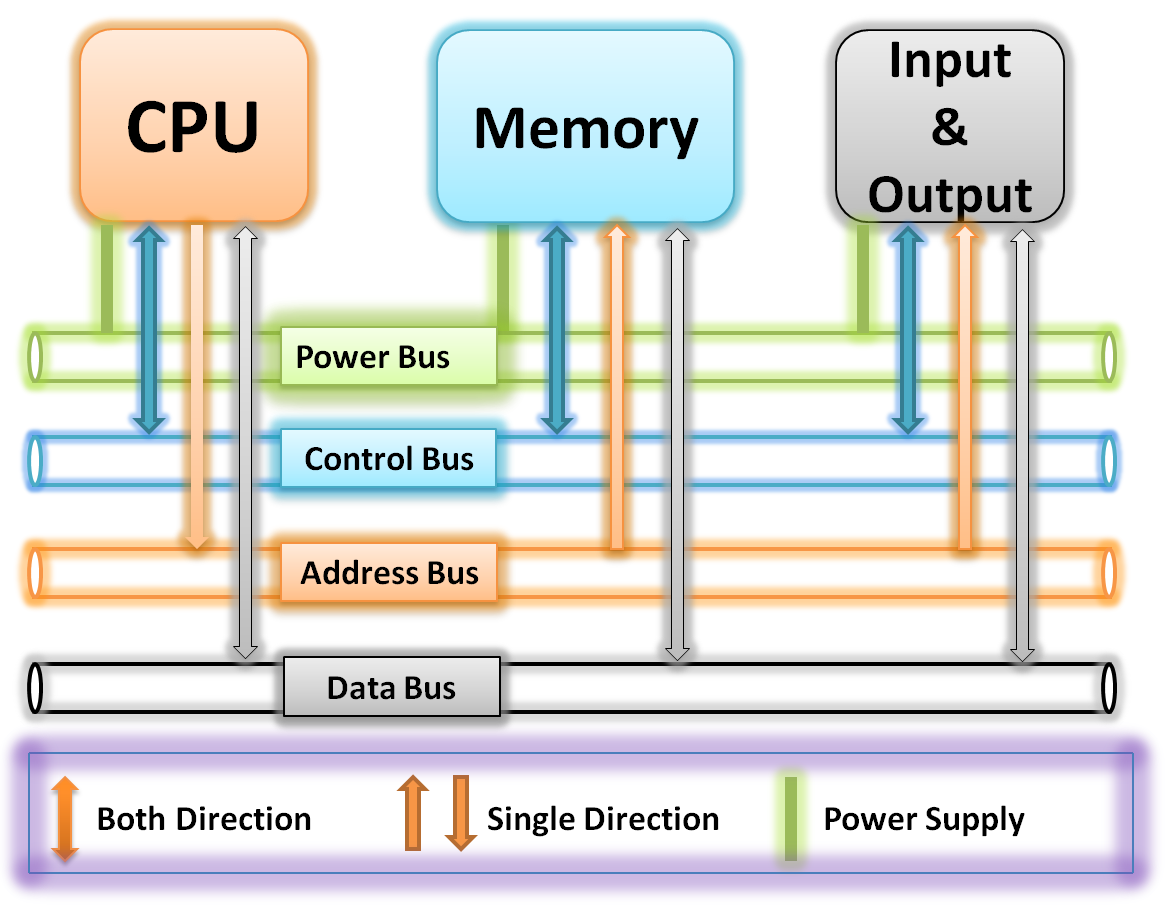

시스템 버스란?

시스템 버스는 컴퓨터 전체와 장치 간에 데이터를 전송하고 공유하는 컴퓨터 아키텍처의 한 측면입니다. 컴퓨터 메인보드 내 프로세서, 메모리, 주변장치들을 서로 연결하여, 시스템이 원활하게 가동되도록, 데이터 전송 역할을 하는 공통의 통로입니다.

시스템 버스의 특정 디자인은 각 특정 컴퓨터 시스템의 스타일, 크기 및 요구 사항에 따라 변경됩니다. 컴퓨터의 시스템 버스를 사용자 정의하거나 시스템이 표준화된 설계를 사용하여 작동하도록 할 수 있습니다. 시스템 버스는 8비트, 16비트, 32비트 등이 될 수 있습니다. 32비트 버스는 한 번에 32비트의 정보를 전송할 수 있음을 의미합니다.

시스템 버스의 종류

시스템 버스를 구성하는 세 가지 유형의 버스가 있습니다. 각 유형의 버스는 정확한 데이터 전송에 기여하는 고유한 명령 집합을 따릅니다. 이 세 가지 유형은 다음과 같습니다.

- 데이터 버스: 데이터 버스는 컴퓨터의 주 프로세서, 메모리 및 기타 모든 내부 하드웨어 구성 요소 간에 실제 데이터를 전달합니다. 컴퓨터 부품이나 장치 사이에서 작동하여 CPU 안팎으로 또는 한 장치에서 다른 장치로 데이터를 전송합니다. 데이터 버스의 크기는 CPU가 한 번에 전송 가능한 데이터의 크기와 같습니다. 데이터를 주고받아야 하기 때문에 양방향 버스입니다.

- 주소 버스: 주소 버스는 시스템에서 데이터가 오고 가는 위치를 알려줍니다. 주소 버스는 CPU와 외부장치와 통신할 때 필요한 주소 정보를 전송할 때 사용한다. 따라서 단방향이고 각 주소선은 주소 비트를 나타내며 주소선은 CPU와 통신할 수 있는 최대 기억장치 용량을 나타냅니다. 주소가 CPU로부터 기억장치 혹은 I/O 장치들로 전송되는 정보이기 때문에 주소 버스는 단방향 버스입니다.

- 주소 버스의 폭이 16비트

- 주소 지정 가능한 최대 기억 장소의 수 = 2**16 = 65,536개

- 바이트 단위 주소 지정일 경우 최대 기억장치 용량 = 64 Kbyte

- 주소 버스의 폭이 24비트

- 주소 지정 가능한 최대 기억 장소의 수 = 2**24 = 16,777,216개

- 바이트 단위 주소 지정일 경우 최대 기억장치 용량 = 16 Kbyte

- 주소 버스의 폭이 16비트

- 제어 버스: 제어 버스는 손상 없이 데이터 전송을 보장하기 위해 버스의 제어, 타이밍 및 조정을 관리하여 시스템 버스가 작동하는 방식을 결정합니다. 현재 수행 중인 작업 종류나 다른 장치에 알릴 때 이용하는 양방향 버스입니다.

- 제어 버스의 가장 기본적인 제어 신호

- 기억장치 쓰기(memory write) 신호 : 버스에 실린 데이터를 주소가 지정하는 기억 장소에 저장되도록 하는 제어 신호

- 기억장치 읽기(memory read) 신호 : 주소가 지정하는 기억 장소의 내용을 읽어서 버스에 실리게 하는 제어 신호

- 입출력 쓰기(I/O write) 신호 : 버스에 실린 데이터를 지정된 I/O 장치로 출력되게 하는 제어 신호

- 입출력 읽기(I/O read) 신호 : 지정된 I/O 장치로부터 데이터를 익어서 데이터 버스에 실리게 하는 제어 신호

- 전송 확인(transfer acknowledge) 신호 : 데이터 전송 동작이 완료되었음을 알려주는 신호

- 제어 버스의 가장 기본적인 제어 신호

버스 중재

시스템 버스를 사용하는 주체를 버스 마스터(Bus Master)라 합니다. 시스템 버스는 한 번에 하나의 마스터만이 이용할 수 있는데, 버스 사용을 요구하는 여러 마스터 중 특정 마스터를 선정해 버스 사용을 승인하고, 나머지 마스터를 대기하도록 하는 과정을 버스 중재(Bus Arbitration)라 합니다.

컴퓨터 시스템에는 버스 중재를 전담하는 장치가 하나 이상 존재하며, 이를 버스 중재기(Bus Arbitor)라 합니다. 버스 중재기와 버스 마스터 간에 전송되는 버스 중재를 위한 각종 신호 역시 제어 버스를 이용해 전송되는데, 제어 버스 중 버스 중재에 사용되는 선들의 집합을 중재 버스(Arbitration Bus)라 부르기도 합니다.

중재 버스를 통해 전달되는 신호는 다음과 같습니다.

- 버스 요구(Bus Request, BREQ)

임의의 버스 마스터가 중재기에게 버스 사용을 요구하는 신호 - 버스 승인(Bus Grant, BGNT)

중재기가 BREQ 신호를 받았을 때 마스터에게 요구에 대해 승인함을 알리는 신호 - 버스 사용 중(Bus Busy, BBUSY)

임의의 버스 마스터가 사용을 요구했을 때 이미 다른 마스터가 버스를 사용 중임을 알리는 신호

인터럽트 버스

CPU와 I/O 간의 비동기적 동작 지원하는 인터럽트 메커니즘을 위한 신호 선들의 집합을 인터럽트 버스(Interrupt Bus)라 부릅니다.

인터럽트 버스는 다음 제어 신호들을 전송한다.

- 인터럽트 요구(Interrupt Request, INTR)

- 인터럽트 확인(Interrupt Acknowledge, INTA)

버스 대역폭

대역폭이란 데이터가 이동하는 버스를 통해 단위 시간당 전송하는 데이터의 크기입니다. 대역폭은 해당 버스의 클록 주기와 데이터 버스의 폭으로 결정됩니다.

즉, 버스 대역폭은 버스를 통해 시간당 전송할 수 있는 데이터의 양입니다.

버스 대역폭 = 버스의 클럭 주파수 x 데이터 버스의 폭

예를 들어

버스의 클록 주파수가 50 Mhz이고 데이터 버스의 폭이 32bit(4Byte)

버스 대역폭은 200 Mbyte/s입니다.

즉, 이 버스를 통하여 초당 2억 바이트의 데이터 전송이 가능합니다.

시스템 버스의 기본 동작

시스템 버스의 동작은 크게 쓰기 동작과 읽기 동작으로 나뉜다.

쓰기 동작(write operation) 순서

- 버스 마스터가 버스 사용권 획득

- 버스를 통해 주소와 데이터를 및 쓰기 신호 전송

읽기 동작(read operation) 순서

- 버스 마스터가 버스 사용권 획득

- 주소와 읽기 신호를 보내고, 데이터가 전송되어 올 때까지 대기

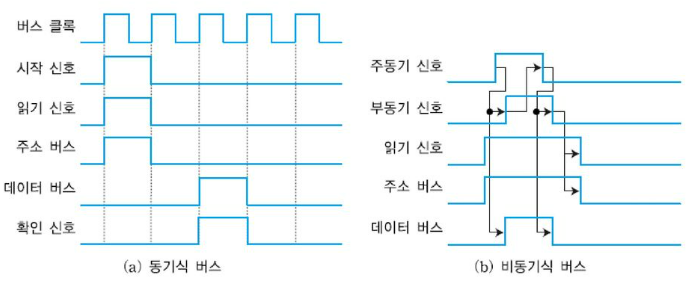

동기식 버스와 비동기식 버스

이러한 시스템 버스의 동작은 그 방식에 따라 두 가지로 나눌 수 있습니다.

- 동기식 버스(Synchronous Bus)

시스템 버스에서 모든 버스 동작이 공통의 버스 클록을 기준으로 발생합니다. - 비동기식 버스(Asynchronous Bus)

버스 동작들의 발생 시간이 관련된 다른 버스 동작의 발생 여부에 따라 결정됩니다.

동기식 버스의 경우 간단한 하드웨어 회로 구조로 구현이 가능하지만, 버스 클록의 주기가 가장 오래 걸리는 버스 동작의 소요 시간을 기준으로 동작 시간이 결정된다는 단점이 있습니다. 그리고 기억장치의 작업이 한 클럭 이상을 소요할 경우 CPU가 그만큼 유휴 시간(Idle time)을 가지게 됩니다.

비동기식 버스의 경우 CPU가 쉬는 시간 없이(자원의 낭비 없이) 작동할 수 있게 되지만 인터페이스 회로가 복잡해지는 단점이 있습니다.