728x90

TDA4VH EVM에는 TYPEC에 연결된 두 개의 레인이 있습니다.

하지만 dtsi에서는 USB3.0 지원을 위해 LANE3만 구성하고 있습니다.

EVM보드 기준 구성이 아닌 LANE2에서 USB3.0 레인 기능을 활성화하려면 아래 변경 작업을 수행해야 합니다.

변경 사항 1

arch/arm64/boot/dts/ti/k3-j784s4-evm.dtsdiff --git a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 492975144..94e6f7702 100644

--- a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -711,13 +711,12 @@ serdes0_pcie_link: phy@0 {

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>, <&serdes_wiz0 2>;

};

-

- serdes0_usb_link: phy@3 {

- reg = <3>;

- cdns,num-lanes = <1>;

+ serdes0_usb_link: phy@2 {

+ reg = <2>;

+ cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

- resets = <&serdes_wiz0 4>;

+ resets = <&serdes_wiz0 3 >,<&serdes_wiz0 4>;

};

};

@@ -780,7 +779,7 @@ &main_navss_intr {

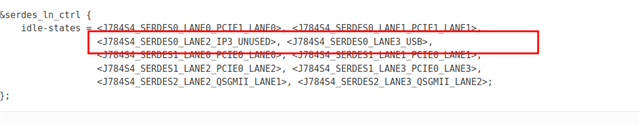

&serdes_ln_ctrl {

idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>,

- <J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

+ <J784S4_SERDES0_LANE2_USB_SWAP>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

<J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

@@ -1229,11 +1228,6 @@ &main_mcan16 {

phys = <&transceiver3>;

};

-&serdes_wiz0 {

- typec-dir-gpios = <&wkup_gpio0 28 GPIO_ACTIVE_HIGH>;

- typec-dir-debounce-ms = <700>; /* TUSB321, tCCB_DEFAULT 133 ms */

-};

-

&usb_serdes_mux {

idle-states = <0>; /* USB0 to SERDES lane 3 */

};

변경 사항 2

include/dt-bindings/mux/ti-serdes.hdiff --git a/include/dt-bindings/mux/ti-serdes.h b/include/dt-bindings/mux/ti-serdes.h

index 91ea9633c..5a6ac4587 100644

--- a/include/dt-bindings/mux/ti-serdes.h

+++ b/include/dt-bindings/mux/ti-serdes.h

@@ -131,7 +131,7 @@

#define J784S4_SERDES0_LANE2_PCIE3_LANE0 0x0

#define J784S4_SERDES0_LANE2_PCIE1_LANE2 0x1

-#define J784S4_SERDES0_LANE2_IP3_UNUSED 0x2

+#define J784S4_SERDES0_LANE2_USB_SWAP 0x2

#define J784S4_SERDES0_LANE2_IP4_UNUSED 0x3

#define J784S4_SERDES0_LANE3_PCIE3_LANE1 0x0

변경 사항 적용 후 빌드

[09] TDA4VH-Q1 Processor SDK

테스트 환경Ubuntu 22.04J78S4XG01EVMJ75S4XG01EVM Processor SDK Version 09_02_00_05 SDK 다운로드아래 링크에서 09_02_00_05 버전 다운https://www.ti.com/tool/download/PROCESSOR-SDK-LINUX-J784S4/09.02.00.05 PROCESSOR-SDK-LINUX-J784S4 S

rorsi.tistory.com

위의 변경 사항을 적용한 후 생성된 DTB를 변경하면, 기존 LANE3 USB는 2.0으로 작동합니다.

728x90

'TI > TDA4VH' 카테고리의 다른 글

| [09] TDA4VH - mcu_i2c0 활성화 (0) | 2024.12.16 |

|---|---|

| [09] TDA4VH - emmc (1) | 2024.12.11 |

| [09] TDA4VH-Q1 - SDCard 이미지 만들기 (0) | 2024.03.17 |

| [09] TDA4VH-Q1 Processor SDK (0) | 2024.03.13 |

![[TDA4VH] USB 3.0 lane 변경](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FXAsJA%2FbtsKKIBcZcy%2FfPyJK62i7U6CTHZt0GZXQ0%2Fimg.png)